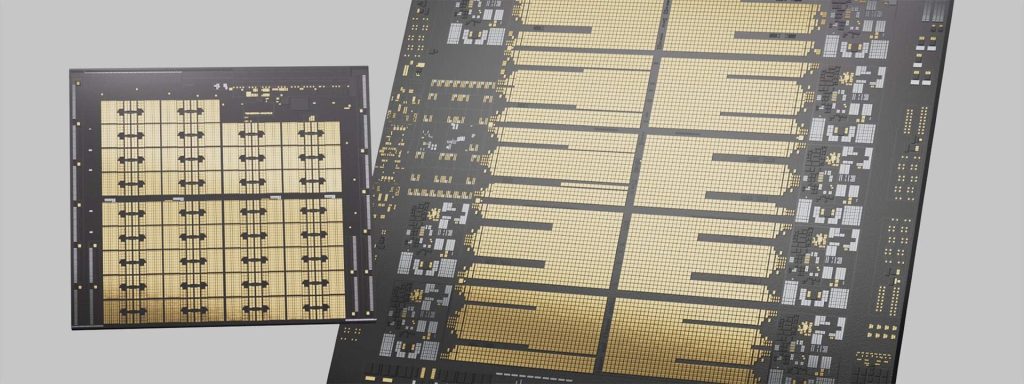

IBM ha presentato le specifiche sull’architettura del prossimo processore IBM Telum II e di IBM Spyre Accelerator in occasione della Hot Chips 2024. Queste nuove tecnologie sono progettate per aumentare significativamente la capacità di elaborazione della prossima generazione di sistemi mainframe IBM Z, contribuendo ad accelerare l’adozione dei modelli AI tradizionali e dei Large Language Models (LLM) anche in tandem, grazie a una nuova metodologia di AI detta di tipo “ensemble”.

Visti i numerosi progetti di AI generativa basati sui Large Language Models, che passano dal “proof-of-concept” alla produzione, la richiesta di soluzioni energeticamente efficienti, sicure e scalabili emerge come priorità chiave. Una ricerca di Morgan Stanley, pubblicata ad agosto, prevede per i prossimi anni un incremento annuo del 75% del fabbisogno energetico dell’AI generativa, arrivando così a utilizzare, nel 2026, una quantità di energia pari a quella consumata dalla Spagna nel 2022. Molti clienti IBM hanno evidenziato l’importanza crescente di effettuare scelte architetturali a supporto di foundation model di dimensioni adeguate e di adottare approcci “hybrid-by-design” per lo sviluppo dei carichi di lavoro AI.

Le principali innovazioni presentate da IBM

- Processore IBM Telum II: Sviluppato a supporto dei sistemi IBM Z di prossima generazione, il nuovo chip IBM presenta, rispetto alla prima generazione dei processori Telum, un incremento di frequenza e capacità di memoria, una cache aumentata del 40%, un acceleratore AI integrato migliorato e una nuova “Data Processing Unit” (Unità di Elaborazione Dati) relativamente annessa. Si prevede che il nuovo processore sia in grado di supportare soluzioni di calcolo a livello enterprise nell’esecuzione dei LLM, in grado di soddisfare le complesse esigenze transazionali del settore.

- Unità di accelerazione IO: Una nuova unità di elaborazione dati (DPU), integrata nel chip del processore Telum II, è stata sviluppata per accelerare su mainframe i complessi protocolli di I/O necessari al networking e all’interazione con lo storage. La DPU semplifica le operazioni di sistema e può migliorare le prestazioni di molteplici componenti chiave.

- IBM Spyre Accelerator: Fornisce ulteriori capacità di elaborazione AI a supporto del processore Telum II. Combinando l’utilizzo dei chip Telum II e Spyre si genera un’architettura scalabile utile a supportare i metodi di “Ensemble AI” – ovvero la pratica di unire più modelli di machine learning o di deep learning agli encoder LLM. Sfruttando i punti di forza di ciascuna architettura, l’ensemble AI può fornire risultati più accurati e affidabili rispetto ai singoli modelli. Il chip IBM Spyre Accelerator, presentato in anteprima alla conferenza Hot Chips 2024, sarà fornito come opzione aggiuntiva. Ogni accelerator chip viene collegato tramite un adattatore PCIe da 75 watt e basato sulla tecnologia sviluppata in collaborazione con IBM Research. Come altre schede PCIe, Spyre Accelerator è scalabile per adattarsi alle diverse esigenze dei clienti.

“La nostra solida roadmap multi-generazione ci consente di essere sempre all’avanguardia nei trend tecnologici, data la crescente domanda di intelligenza artificiale”, ha affermato Tina Tarquinio, VP, Product Management, IBM Z e LinuxONE. “Il processore Telum II e Spyre Accelerator sono progettati per offrire soluzioni computazionali aziendali ad alte prestazioni, sicure e più efficienti dal punto di vista energetico. Dopo anni di sviluppo, queste innovazioni saranno introdotte nella nostra piattaforma IBM Z di prossima generazione in modo che i clienti possano sfruttare i Large Language Models e l’AI generativa su vasta scala.”

Il processore Telum II e l’IBM Spyre Accelerator saranno realizzati da Samsung Foundry, partner storico di IBM, e basati sul proprio nodo di processo a 5 nm ad alte prestazioni ed efficienza energetica. Questa sinergia supporterà una serie di casi di utilizzo avanzati basati sull’intelligenza artificiale al fine di accrescere il valore aziendale e conferire una maggiore competitività. Grazie ai metodi di intelligenza artificiale ensemble, i clienti potranno ottenere previsioni più rapide e precise. La potenza di elaborazione combinata darà un forte stimolo verso l’adozione dell’AI generativa in molteplici situazioni.

Di seguito alcuni esempi:

- Identificazione delle frodi nelle richieste di risarcimento assicurativo: Miglioramento del rilevamento delle frodi nei sinistri delle assicurazioni immobiliari grazie all’ensemble AI, che combina LLM e reti neurali tradizionali per ottenere maggiori prestazioni e accuratezza.

- Antiriciclaggio avanzato: Rilevamento avanzato di attività finanziarie sospette, supportando la conformità ai requisiti normativi e mitigando il rischio di reati finanziari.

- Assistenti AI: Per accelerare il ciclo di vita delle applicazioni, il trasferimento di conoscenze e competenze, la spiegazione e la trasformazione del codice, e molto altro ancora.

Specifiche e parametri di performance

Processore Telum II: Basato su otto core ad alte prestazioni funzionanti a 5.5 GHz, dotati di 36 MB di cache L2 ciascuno, per un aumento complessivo del 40% della cache disponibile sul singolo chip, pari a 360 MB. Anche la cache virtuale di Livello 4, condivisa tra i processori di uno stesso drawer, risulta aumentata del 40% rispetto alla generazione precedente, per un totale di 2.88 GB per drawer.

L’acceleratore di AI integrato consente di effettuare inferenze AI sulle transazioni con basse latenze e throughput elevati, per esempio migliorando il rilevamento delle frodi durante le transazioni finanziarie. La capacità di calcolo del singolo acceleratore AI risulta quadruplicata rispetto alla generazione precedente.

La nuova unità di accelerazione I/O DPU, integrata nel chip Telum II, è stata progettata per migliorare la gestione dei dati grazie a un aumento della densità di I/O del 50%.

Questo avanzamento permette di migliorare l’efficienza e la scalabilità complessive dei sistemi IBM Z, rendendoli adatti a gestire i workload AI su vasta scala e le applicazioni ad alta intensità di dati richiesti oggi dalle aziende.

Spyre Accelerator: Acceleratore di livello enterprise, sviluppato ad-hoc, offre capacità elaborativa scalabile richiesta dai modelli di intelligenza artificiale complessi e permette l’adozione dell’AI generativa in molteplici casi d’uso.

Questo acceleratore è in grado di operare in cluster di 8 schede all’interno di un normale I/O Drawer, per una memoria complessiva di 1 TB, in grado di supportare i carichi di lavoro AI richiesti dal mainframe, pur essendo progettato per consumare non più di 75W per scheda.

Ogni chip avrà 32 core di calcolo in grado di supportare dati di tipo int4, int8, fp8 e fp16 per applicazioni di intelligenza artificiale a bassa latenza e alto throughput.

Disponibilità

Telum II sarà il processore centrale alla base della prossima generazione di piattaforme IBM Z e IBM LinuxONE, disponibile per i clienti IBM Z e LinuxONE nel 2025. Anche la disponibilità di IBM Spyre Accelerator, attualmente in anteprima tecnica, è prevista per il 2025.